## ALUPE UNIVERSITY CONTEST ... Bastion of Knowledge....

P. O.Box 845-50400 Busia(K) principal@auc.ac.ke Tel: +254 741 217 185 +254 736 044 469 off Busia-Malaba road

OFFICE OF THE DEPUTY PRINCIPAL ACADEMICS, STUDENT AFFAIRS AND RESEARCH

# UNIVERSITY EXAMINATIONS 2019 /2020 ACADEMIC YEAR

SECOND YEAR FIRST SEMESTER REGULAR EXAMINATION

FOR THE DEGREE OF BACHELOR OF SCIENCE IN COMPUTER SCIENCE

**COURSE CODE:**

**COM 217**

**COURSE TITLE:**

**ELECTRONICS I**

DATE: 4<sup>th</sup> December 2019

TIME: 2:00PM-5:00PM

### INSTRUCTION TO CANDIDATES

• SEE INSIDE

THIS PAPER CONSISTS OF PRINTED PAGES

PLEASE TURN OVER

#### **COM 217: ELECTRONICS I**

**DURATION: 3 Hours**

STREAM: BSc (Comp. Scie.)

#### **INSTRUCTIONS TO CANDIDATES**

i. Answer the questions **ONE** and **TWO** in **SECTION** A and **ANY OTHER THREE** questions in **SECTION** B.

#### **SECTION A (24 MARKS)**

#### **Question One (12 Marks)**

a) Distinguish between an intrinsic semiconductor and extrinsic semiconductor. (2 Marks)

b) Sketch diode circuit in forward bias and reverse bias connection. (4 Marks)

c) Define the following terms that are often used with the *pn* junction.

i)Breakdown voltage(1 Mark)ii)Knee voltage(1 Mark)iii)Forward current(1 Mark)iv)Leakage current(1 Mark)

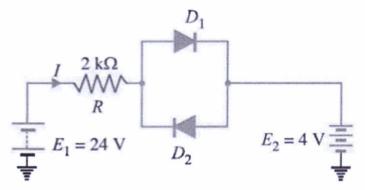

d) Determine the current I in the circuit shown below. Assume the diodes to be made of silicon and forward resistance of diodes to be zero. (2 Marks)

#### Question Two (12 Marks)

a) Describe the working of *npn* transistor action in detail whose net effect is

$I_E$  is large,  $I_C$  is large and  $I_B$  very is small. (2 Marks)

b) i) Draw the input and output characteristics of *CE* connection. (4 Marks)

- ii) Establish the relationship  $I_C = \frac{\alpha_{DC}}{1 \alpha_{DC}} I_B \frac{1}{1 \alpha_{DC}} I_{CO}$ . (2 Marks)

- c) Draw and label schematic symbols of P-channel and N-channel JFETs. (2 Marks)

- d) Distinguish between a TRIAC and DIAC semiconducting devices. (2 Marks)

#### **SECTION B (36 MARKS)**

#### Question Three (12 Marks)

- a) Draw and explain the I-V characteristics of a pn junction. (5 Marks)

- b) Draw the equivalent circuit of an ideal zener diode in the breakdown region. (2 Marks)

- c) State three applications of a zener diode. (3 Marks)

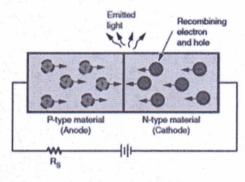

- d) i) A forward biased light-emitting diode (LED) circuit is shown below. Explain the working of LED diode. (2 Marks)

ii) Draw a reverse biased photodiode circuit and describe briefly its working operation.

(2 Marks)

#### **Question Four (12 Marks)**

a) Define transistor biasing

(1 Mark)

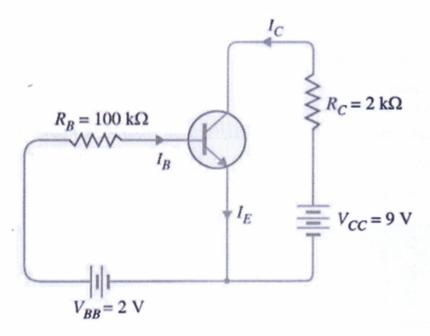

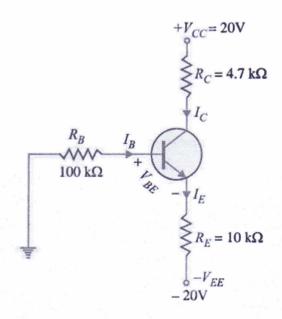

b) The figure below shows biasing with base resistor method.

- i) Determine the collector current  $I_C$  and collector-emitter voltage  $V_{CE}$ . Neglect small base-emitter voltage. Given that  $\beta = 50$ . (2 Marks)

- ii) If  $R_B$  in this circuit is changed to  $50\text{K}\Omega$ , find the new operating point. (2 Marks)

c) For the emitter bias circuit shown below, find  $I_E, I_C, V_C$  and  $V_{CE}$  for  $\beta$  = 85 and  $V_{BE} = 0.7 \, V. \tag{4 Marks}$

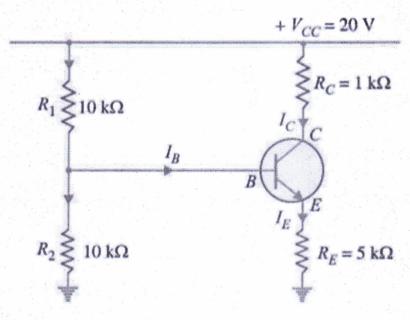

d) Calculate the emitter current in the voltage divider circuit shown below. Also find the value of  $V_{CE}$  and collector potential. (4 Marks)

#### **Question Five (12 Marks)**

a) Explain with the aid of labelled circuit diagrams how half-wave rectification is achieved.

(4 Marks)

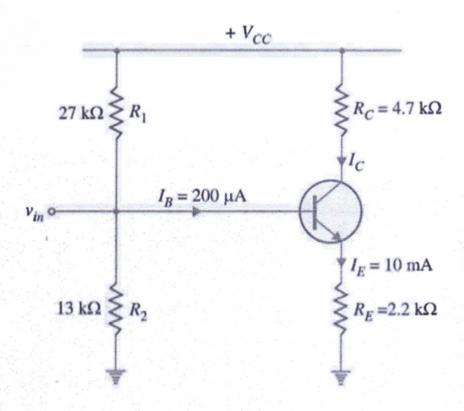

c) For the transistor amplifier shown in the figure below,  $R_1 = 10k\Omega, \ R_2 = 5k\Omega, R_C = 1\,k\Omega, \ R_E = 2\,k\Omega \ \text{and} \ R_L = 1\,k\Omega \,.$

- i) Draw d.c load line (2 Marks)

- ii) Determine the operating point (2 Marks)

- d) What is the meaning of phase reversal in reference to single stage transistor? (1 Mark)

#### Question Seven (12 Marks)

- a) What do you understand by multistage amplifier? (1 Mark)

- b) Explain the following terms

- i) Frequency response (1 Mark

- ii) Decibel gain (1 Mark)

- iii) Bandwidth (1 Mark)

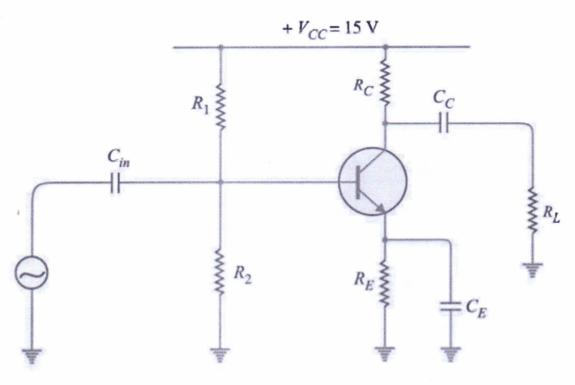

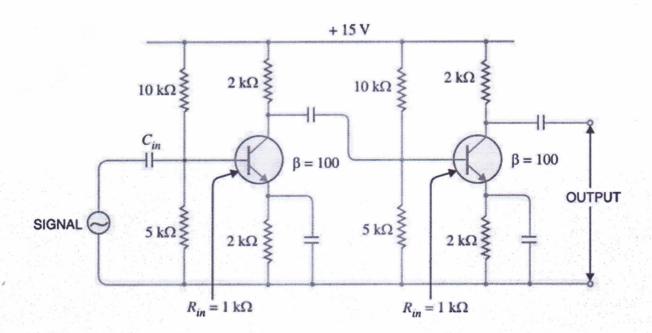

- c) The figure below shows two-stage RC coupled amplifier.

If the input resistance  $R_{in}$  of each stage is 1 k $\Omega$  and  $\beta$  = 100, find:

| i)   | Voltage gain of first stage  |  | (2 Marks) |

|------|------------------------------|--|-----------|

| ii)  | Voltage gain of second stage |  | (1 Mark)  |

| iii) | Total gain                   |  | (1 Mark)  |

- d) Distinguish between a JFET and MOSFET. (2 Marks)

- e) What is the difference between a depletion MOSFET and an enhancement MOSFET?

(2 Marks)

\*\*\*\*\*\*\*\*\*\*\*